SCCC: A plataforma

Esta é uma das motherboards iniciais. A motherboard actual, da plataforma “Rocky Lake” tem mais opções, como podem ver nas imagens a seguir, mas esta imagem server para mostrar algumas coisas.

O principal nesta imagem é o chipset, que como podem ver não é comum. Os mais atentos vão repara que diz “Virtex 5”, isto porque na verdade não há um chipset da Intel para esta plataforma.

O que a Intel fez foi colocar um FPGA (um chip programável) da Xilinx, do modelo Virtex 5.

Isto permite à Intel uma grande flexibilidade a nível do chipset, visto que sendo um chip programável, podem ir adicionando features ao longo do tempo.

O segundo aspecto é os slots de memória Ram. O SCCC tem quatro controladores de memória DDR3, em que cada controlador tem 2 slots de Ram.

A plataforma aceita até ao máximo de 64 GB de RAM, mas estes controladores de memória e como a memória é gerida é bem mais complicado que o comum, como verão durante este artigo.

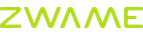

Esta é a mais recente plataforma, de seu nome “Rocky Lake”.

A Intel forneceu mais de 100 destes sistemas a 80 parceiros de todo o mundo e estão a participar ao todo 300 investigadores neste projecto.

Existem também 40 destes servidores num dos Datacenters da Intel, para os investigadores que têm acesso, ligarem-se remotamente.

No entanto este computador não é autónomo. Para o gerir é preciso um segundo computador que se ligue via cabo de rede ao BMC que controla o computador.

Na imagem também é possível ver o que o chipset já suporta. Quatro placas de rede gigabit, PCI-Express X4, duas portas série e uma ligação por cabo série.

SCCC: Visão geral

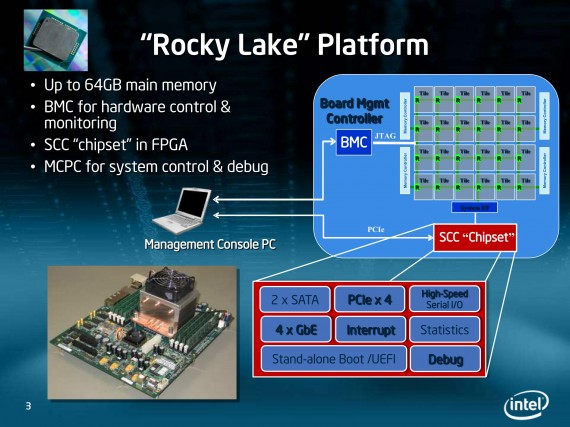

Neste slide pode-se ver o processador, que usa um socket LGA com 1567 pinos e a plataforma do lado direito.

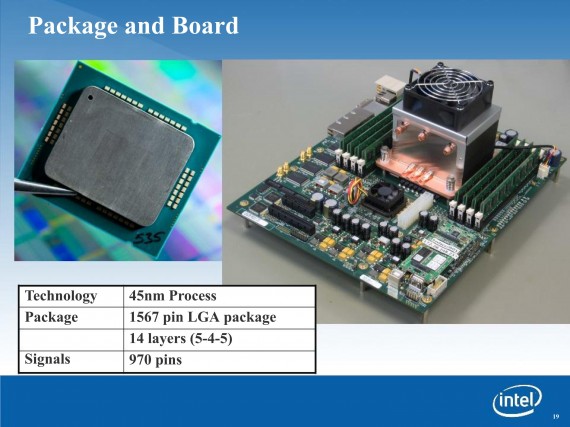

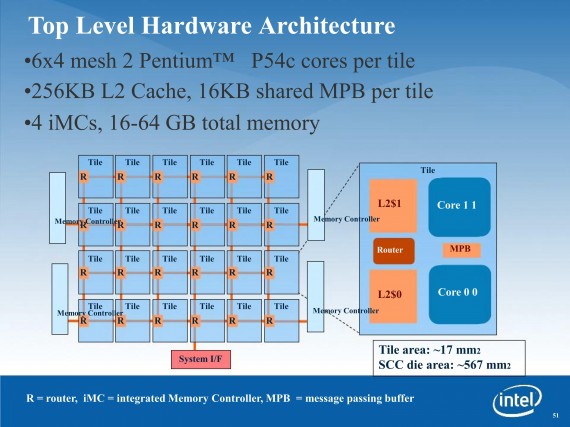

Esta é a visão geral do processador.

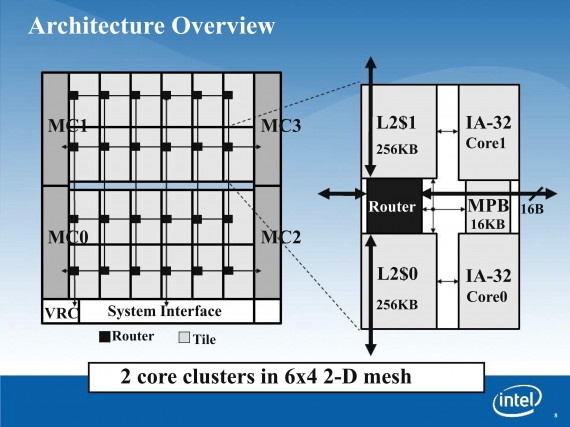

O processador é composto por duas partes, em que cada parte tem 12 “tiles”. Podemos ver nesta imagem que cada “tile” tem um router para comunicar com as outras tiles.

Podemos ver também os quatro controladores de memória, que servem as “tile”.

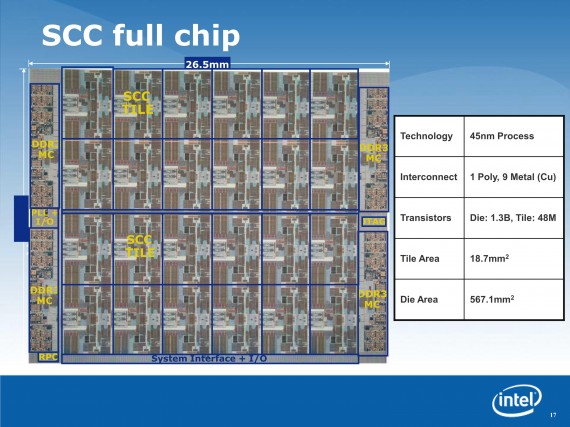

Esta é outra visão do processador, com alguns detalhes técnicos.

Visto que o processador saiu em 2009, usa ainda o processo de fabrico de 45 nm.

Ao todo o processador tem 1.3 mil milhões de transístores e cada “tile” 48 milhões.

A área de cada “tile” é de apenas 18.7 milímetros quadrados, mas juntando tudo dá um valor impressionante de 567.1 milímetros quadrados.

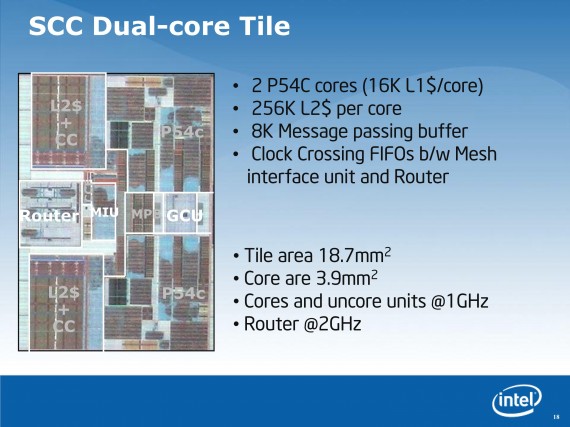

Aqui temos pela primeira vez uma visão ao pormenor de cada “tile”.

Dá para perceber facilmente que uma “tile” do SCCC é mais complexa que o Tera Chip, mas manteve-se a ideia do router.

Cada “tile” tem dois cores Pentium P54C, mas com alterações.

A cache L1 de instruções e de dados passou de 8 para 16 KB e cache L2 de 256 KB não é externa, mas sim interna.

Entre os dois cores, existe um buffer de 16 KB para comunicação entre os dois. Normalmente cada core usa metade desse valor, mas isso pode ser alterado.

Podemos ver também que a área de cada core é muito pequena, isto porque se está a usar um core muito simples para os dias de hoje.

A nível de velocidades, o normal é o router funcionar a 2 Ghz e o os cores a 1 Ghz, mas este valor pode ser superior, caso não tivessem imposto um limite de 125 W, ou inferior, com power management, quando um core ou router não está a ser utilizador.

Aqui podemos ver como é composta a rede, visto que cada router usa uma matriz 4X4.

Os controladores de memória podem ter de 16 a 64 GB e isso dita o valor que cada processador vai ter em memória privada.

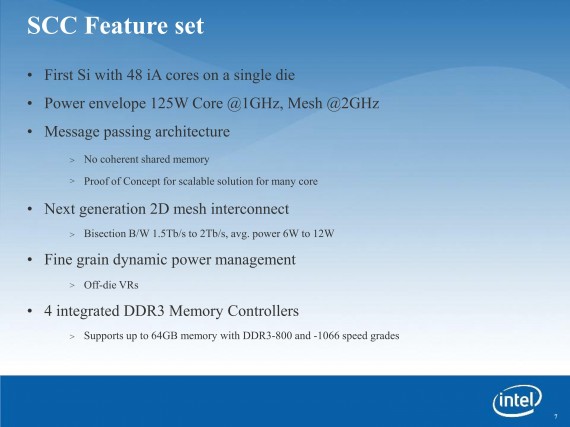

Aqui temos um resumo das principais características.

48 cores x86 independentes e pela primeira vez vemos que a memória não é coerente, o que para um sistema multi processador é algo estranho de se perceber à primeira vista.

Vemos também que a rede 2D, a 2 Ghz tem uma bandwidth total de 2 Tbits a consumir 12 W.

Existe também um controlo pormenorizado do power management do processador e que os controladores de memória suportam até DDR3-1066.

Neste slide vemos mais uma vez os 24 “tiles” e a composição de cada “tile”.

O que se evidencia mais neste slide é o router, partilhado por dois cores, que têm um buffer para comunicarem entre eles.